tämä artikkeli keskittyy oppimaan, miten Mikrocontroller core on suunniteltu ja tarkoitettu vain opetuskäyttöön. Ole hyvä ja vieraile www.zilog.com ja tarkista valmistajan tuotelinjan valita mikrokontrolleri, joka sopii projektin tarpeisiin (alkaen kahdeksan-bittinen Z8 Encores! ja eZ80 Acclaims 32-bittinen ARM Cortex-M3 perustuu ZNEO32! joka sisältää kehittyneet Moottorin ohjausominaisuudet).

rakkaussuhteeni mikrokontrollereihin ja mikroprosessoreihin alkoi vuonna 1988, kun olin suorittamassa teknistä tutkintoa CEFET-PR: ssä (nelivuotinen Brasilialainen keskiasteen/teknillinen koulu ja yliopisto, joka sijaitsee Curitibassa). Aloitin opettelemalla perusasiat tutustuessani klassiseen Zilog Z-80: een (Kuva 1a).

kuva 1A.Zilog Z-80A (Wikimedia Commons).

Pikakelaa eteenpäin ohjelmointiuralla, johon kuului mikrokontrolleriohjelmointia käsittelevien kirjojen kirjoittaminen (KS.resurssit), pienen Suunnittelutalon (ScTec) perustaminen ja valmistumisen jälkeinen ohjelma CEFET-SC: ssä (toinen Brasilialainen yliopisto florianopoliksessa). Tämä tapahtui vuonna 2008, jolloin olin enemmän tekemisissä ohjelmoitavan logiikan ja VHDL: n kanssa ja uteliaisuuteni oli huipussaan. Vuosia myöhemmin 2016, löysin erittäin edullinen FPGA (Field-Programmable Gate Array) kit ja päätti antaa sille mahdollisuuden, ja alkoi oppia lisää FPGA tekniikka.

mikä olisikaan parempaa kuin pehmopornon suunnittelu, jossa voisi oppia lisää itse VHDL: stä (VHSIC-laitteiston kuvauskieli), FPGAs: ista ja mikroprosessoriytimistä? Päädyin valitsemaan modernin Z-80 sukulaisen: Zilog Z8 Encore! (alias, eZ8; Kuva 1b).

kuva 1B. Zilog eZ8.

se on kahdeksanbittinen mikrokontrolleriydin, jossa on yksinkertainen-mutta tehokas — ohjesarja ja erittäin mukava on — chip debuggeri. Kevyt IDE (integrated development environment) ja ilmainen ANSI C-kääntäjä on erinomainen projekti oppia (ja myös opettaa) sulautetuista järjestelmistä.

ennen kuin sukellat ydintoiminnan, VHDL: n ja FPGAs: n syvyyksiin, vilkaiskaamme Zilog Z8 encorea! ominaisuus.

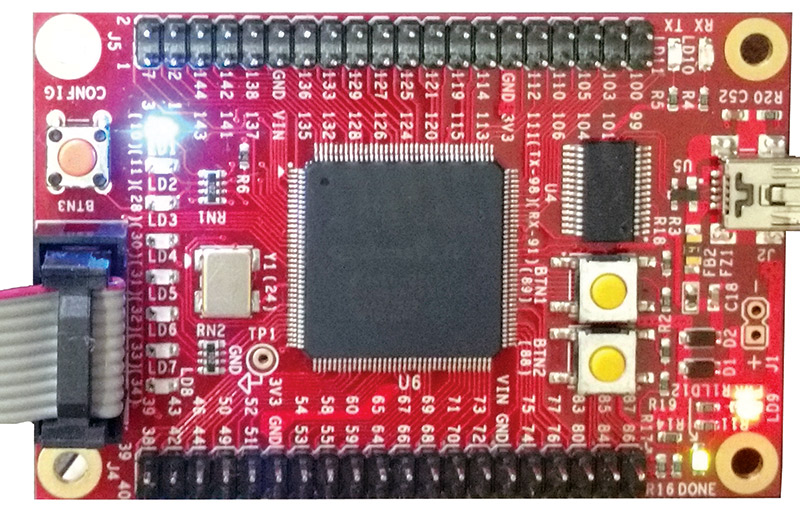

kuva 1c. FPz8 FPGA: ssa.

Zilog Z8 Encore!

Ez8 on kahdeksanbittinen mikrokontrolleriperhe, joka perustuu Zilogin menestyksekkääseen Z8-perheeseen ja suureen Z-80-perintöön. Siinä on Harvardin CISC-kone, jossa on enintään 4 096 tavua RAM-muistia (tiedostorekisteri ja erikoistoimintarekisterien alue), enintään 64 KB ohjelmamuistia (yleensä Flash-muisti) ja enintään 64 KB datamuistia (RAM). EZ8-ydin sisältää myös vektoroidun keskeytysohjaimen, jossa on ohjelmoitava prioriteetti ja on-chip debuggeri, joka kommunikoi isäntätietokoneen kanssa asynkronisella sarjaviestinnällä. Nämä mikrokontrollerit ovat täynnä erittäin mukava perifeerinen sarja, vaihtelevat monipuolinen 16-bittinen ajastimet moottorin ohjaus ajastimet, useita UARTs (IrDA valmis) USB-laitteet, ja paljon muuta (käy www.zilog.com voit tarkistaa koko tuotelinjan).

ez8-ohjelmointimallin yksi merkittävä piirre on kiinteän varaajan puuttuminen. Sen sijaan mikä tahansa 4 096 mahdollisesta RAM-osoitteesta voi toimia Akkuna. Suoritin käsittelee päämuistiaan (tiedosto ja SFRs – special function registers-area) suurena PROSESSORIREKISTERIEN joukkona. Tämän saavuttamiseksi RAM on jaettu rekisteriryhmiin (kussakin on 256 ryhmää 16 toimivaa rekisteriä). Ohje toimii yleensä yhden työrekisteriryhmän sisällä, jonka valitsee SFR nimeltä RP (register pointer). Huomaa, että kaikki SFR: t sijaitsevat RAM-muistin viimeisellä sivulla (osoitteet alkaen 0xf00-0xFFF).

ohjejoukossa on 83 erilaista ohjetta, jotka on jaettu kahteen opcode-sivuun. Se sisältää tavanomaiset ohjeet perustoimintoihin, kuten yhteenlasku, vähennyslasku, loogiset operaatiot, tietojen käsittelyohjeet, siirtoohjeet, virtauksen muutosohjeet, jotkut 16-bittiset ohjeet, bittitestaus ja manipulointi, 8×8-kertolasku jne.

ohjelman muistialue on järjestetty siten, että ensimmäiset osoitteet on omistettu erityistarkoituksiin. Osoitteet 0x0000 ja 0x0001 on omistettu asetusvaihtoehdoille; osoitteet 0x0002 ja 0x0003 tallentavat nollausvektorin; ja niin edelleen. Taulukossa 1 esitetään ohjelman muistin organisaatio.

| 0x0000 | Option bytes |

| 0x0002 | Reset vector |

| 0x0004 | WDT vector |

| 0x0006 | Illegal instruction vector |

| 0x0008 to 0x0037 | Interrupt vectors |

| 0x0038 to 0xFFFF | User program memory area |

TABLE 1. Simplified program memory organization.

joissakin laitteissa on myös toinen tietoavaruus (enintään 65 536 osoitetta), johon pääsee vain käyttämällä LDE/LDEI-ohjeita. Tätä aluetta voidaan käyttää vähemmän käytettyjen tietojen tallentamiseen (koska lukeminen/kirjoittaminen siihen on hitaampaa kuin RAM/SFR-alue).

FPz8

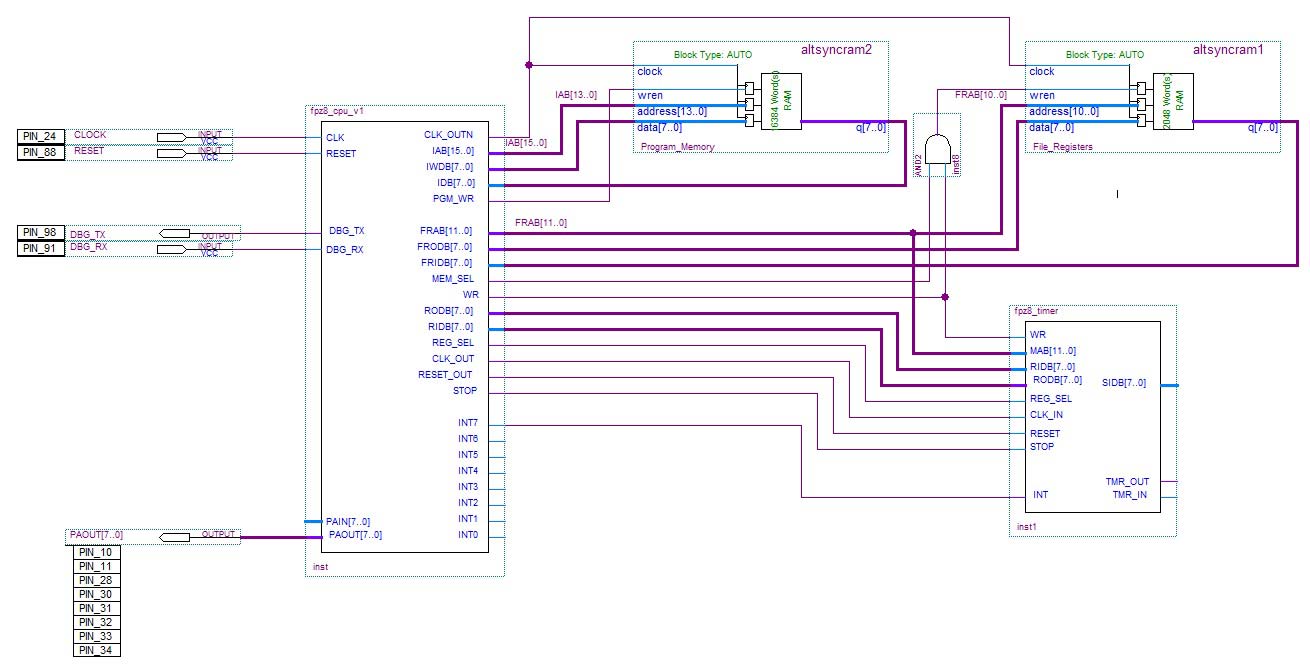

fpz8: n ensimmäinen toteutus käyttää hyvin konservatiivista ja kovalevyistä suunnittelumallia, jossa on kaksi pääväylää: toinen ohjelmamuistille ja toinen rekisterimuistille. Koska päätin olla sisällyttämättä tietojen muistialuetta, LDE/LDEI-ohjeita ei toteuteta.

ohjelman muistiväylät koostuvat 16-bittisestä ohjeosoiteväylästä (IAB), kahdeksanbittisestä ohjeohjausdataväylästä (IDB tietojen lukemiseen ohjelman muistista), kahdeksanbittisestä ohjeadataväylästä (IWDB tietojen kirjoittamiseen ohjelmamuistiin) ja pgm_wr-signaalista, joka ohjaa kirjoittamista ohjelmamuistiin. FPz8 sisältää 16 384 tavua ohjelman muistia, joka on toteutettu synchronous block RAM-muistilla (eli ohjelman muistin sisältö katoaa, kun laite sammutetaan).

viisi rekisterialuebussia käsittävät kolme tiedostorekisterialuetta (user RAM) varten ja kaksi muuta erikoistoimintarekistereille omistettua väylää. On tärkein 12-bittinen tiedosto Rekisteri osoiteväylä (FRAB), kahdeksan-bittinen tiedosto Rekisteri input data bus (FRIDB), kahdeksan-bittinen tiedosto register output data bus (frodb), kahdeksan-bittinen Rekisteri input data bus (ridb), ja lopuksi kahdeksan-bittinen Rekisteri output data bus (RODB) kirjoitettavaksi SFRs. Fpz8 sisältää 2 048 tavua käyttäjän RAM-muistia, joka on toteutettu synkronisella block RAM-muistilla.

kuvassa 2 on lohkokaavio FPz8: sta; näet CPU, kaksi muistiyksikköä (toinen ohjelman tallennukseen ja toinen tietojen tallennukseen), ja myös ulkoinen ajastinmoduuli.

kuva 2. Fpz8 lohkokaavio.

huomaa, että en käytä kaksisuuntaisia linja-autoja yhteenliitäntöihin tässä projektissa. Yksisuuntaiset linja-autot ovat yksinkertaisempia käyttää, vaikka ne ovat vähemmän tilatehokkaita.

FPz8: n VHDL-kuvaus on suuri ja hieman monimutkainen, joten aion jakaa sen toiminnan joihinkin moduuleihin ymmärrettävyyden helpottamiseksi:

- Instruction joneing engine

- Instruction dekoodaus

- keskeytä käsittely

- Debugger

Instruction Joneing Engine

ohjeiden hakeminen on jokaisen suorittimen ensisijainen tehtävä. Fpz8: n Harvard-arkkitehtuuri mahdollistaa samanaikaisen noutamisen ja datan käytön (johtuen erillisistä väylistä opetusta ja dataa varten). Tämä tarkoittaa, että suoritin voi hakea uuden käskyn, kun toinen lukee tai kirjoittaa tietomuistiin.

Ez8: ssa on vaihtelevan pituinen opetussana (opetuksen pituus vaihtelee yhdestä tavusta viiteen tavuun; jotkut ohjeet ovat pitkiä, mutta juoksevat nopeammin kuin toiset. Näin BRK-ohjeen pituus on yksi tavu ja se kulkee kahdessa syklissä, kun taas LDX IM,ER1 on neljä tavua pitkä ja toimii kahdessa kellosyklissä.

Joten, miten voimme onnistuneesti purkaa kaikki nämä ohjeet? Jossa on käskyjono; eli mekanismi, joka pitää hakemassa tavuja ohjelman muistista ja tallentamassa ne kahdeksan tavun joukkoon:

if (CAN_FETCH= ”1”) sitten

if (IQUEUE.FETCH_STATE=F_ADDR) sitten

FETCH_ADDR := PC;

IAB <= PC;

IQUEUE.WRPOS: = 0;

IQUEUE.RDPOS: = 0;

IQUEUE.CNT := 0;

IQUEUE.FETCH_STATE: = F_READ;

else

if (IQUEUE.FULL= ”0”) sitten

IQUEUE.JONO(IQUEUE.WRPOS): = IDB;

FETCH_ADDR:= FETCH_ADDR + 1;

IAB < = FETCH_ADDR;

IQUEUE.WRPOS: = IQUEUE.WRPOS + 1;

IQUEUE.CNT: = IQUEUE.CNT + 1;

end if;

end if;

end if;

if (IQUEUE.CNT=7) sitten IQUEUE.FULL:= ”1”; else IQUEUE.FULL:= ”0”;

end if;

listaus 1. Käskyjonomoottori.

hakemista ohjataan pääkäyttösignaalilla (CAN_FETCH), joka voidaan poistaa käytöstä joissakin erityistapauksissa (keskeytä käsittely, LDC/LDCI-ohjeet tai debuggerin käyttö). On myös rakenne (IQUEUE), joka tallentaa useita sisäisiä parametreja (hakee tila, lukea ja kirjoittaa osoittimia, jono array itse, laskuri, ja täysi indikaattori).

jonolaskuria (CNT) käytetään jonossa käytettävän (luettavan) tavun määrittämiseen. Dekooderivaihe käyttää tätä numeroa varmistaakseen, että haluttu määrä tavuja ohjeelle on jo saatavilla jonossa.

Ohje dekoodaus

tässä tapahtuu varsinainen taikuus. Ohjeen dekooderi lukee opcodes-koodeja käskyjonosta ja muuntaa ne vastaaviksi toiminnoiksi.

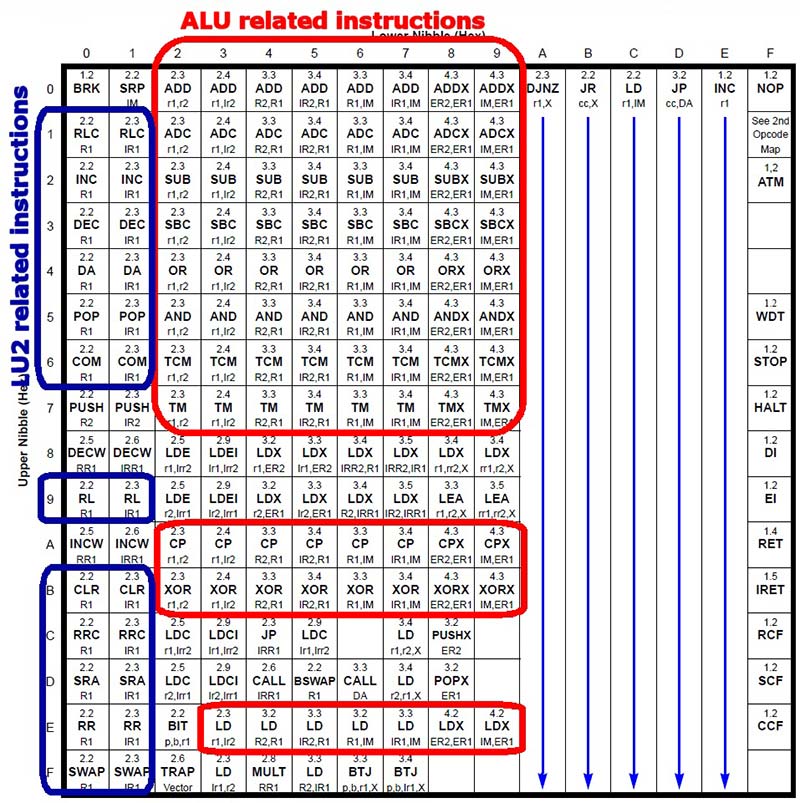

Instruction dekooderin suunnittelu aloitettiin selvittämällä kaikkien ohjeiden ja osoitteiden välinen suhde. Ensi näkemältä on helppo nähdä, että jotkin ohjeet (kuva 3) on ryhmitelty sarakkeittain (DJNZ,JR cc, X,LD r1, IM,JP cc, DA Ja INC r1). INC r1-ohjeen dekoodaus on yksinkertainen: näissä yksitavuisissa ohjeissa korkea näykkäisy määrittää lähde-/kohderekisterin ja alempi näykkäisy määrittää itse ohjeen (0xE).

kuva 3. Opcodes ryhmittäin.

useimmat ohjeet voidaan luokitella joidenkin perussääntöjen mukaan:

- sarakkeet (opcode alempana) määrittävät yleensä osoitetilan: Sarake 0x9 ohjeet, esimerkiksi, käyttävät enimmäkseen IM, ER1 osoitetila ja ovat neljä tavua pitkä (toinen tavu on välitön operandi ja kaksi viimeistä tavua ovat määränpään laajennettu osoite).

- rivit (opcode-koodin suurempi napautus) määrittävät yleensä operaation: 0x0-rivin ohjeet ovat useimmiten yhteenlaskuoperaatioita, 0x2-rivin ohjeet ovat useimmiten vähennysoperaatioita ja niin edelleen.

jos tarkastelemme riviä 0x1, voimme nähdä, että sarakkeet 0x0 ja 0x1 ovat RLC-ohjeita, ja sarakkeet 0x2-0X9 ovat ADC-ohjeita. Niin, voimme suunnitella ALU, joka ottaa näykkäisy syötteenä (korkeampi näykkäisy opcode) ja purkaa sen vastaavasti. Vaikka tämä toimisi sarakkeet 0x2 – 0X9, tarvitsemme toisen lähestymistavan kaksi ensimmäistä saraketta.

tästä syystä päädyin kirjoittamaan kaksi yksikköä: yhden ALU: n, joka keskittyy useimpiin aritmeettisiin ja loogisiin ohjeisiin; ja toisen yksikön (looginen yksikkö 2 eli LU2), joka suorittaa muut sarakkeissa 0x0 ja 0x1 esitetyt operaatiot (kaikki sarakkeissa näkyvät operaatiot eivät ole LU2: n suorittamia). Sekä ALU: n että LU2: n toimintakoodit valittiin vastaamaan Kuvassa 3 esitettyjä opcode-rivejä.

toinen tärkeä yksityiskohta on, että kaikki saman sarakkeen ja ryhmän ohjeet ovat tavuina samankokoisia, joten ne voidaan dekoodata samassa dekooderiosiossa.

dekooderin suunnittelussa hyödynnetään suurta äärellistä valtiokonetta (FSM), joka etenee jokaisella kellotapilla. Jokainen ohje alkaa CPU_DECOD stat: ssa. Tässä dekooderi todella purkaa opcodes, valmistelee bussit ja sisäiset tukisignaalit, ja vaiheet muihin suoritustiloihin. Kaikista näistä valtioista kaksi on laajalti käytössä paljon ohjeita: CPU_OMA ja CPU_OMA2. Arvaatko miksi? Jos sanoit, koska ne ovat sukua ALU ja LU2, olet aivan oikeassa!

OMA on lyhenne yhdestä Muistiyhteydestä ja se on viimeinen tila kaikille ALU: hun liittyville ohjeille (ADD, ADC, ADDX, ADCX, SUB, SBC, SUBX, SBCX, tai, ORX, ja, ANDX, XOR, XORX, CP, CPC, TCM, TCMX, TM, TMX sekä eräät LD: n ja LDX: n muunnelmat). Toisaalta CPU_OMA2 on viimeinen tila kaikille LU2: een liittyville ohjeille (RLC, INC, DEC, DA, COM, RL, CLR, RRC, SRA, SRL, RR ja SWAP).

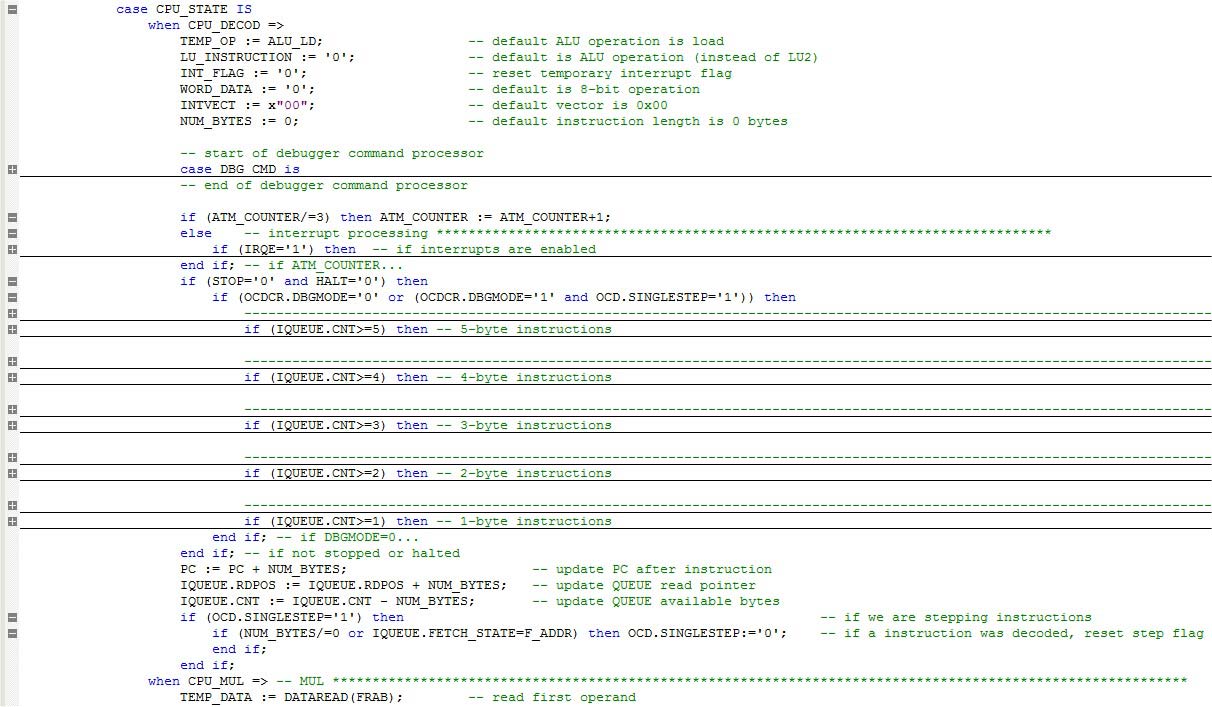

Katsotaanpa nyt cpu_decod-tilan sisälle. KS.Kuva 4.

kuva 4. CPU_DECOD-tila.

cpu_decod-tilassa voidaan nähdä, että toimintaa tapahtuu paljon. Alussa osa väliaikaisista muuttujista alustetaan oletusehtoon. Huomaa, että NUM_BYTES on erittäin tärkeää, koska se ohjaa kuinka monta tavua kulutti opetusta dekooderi. Sen arvoa käytetään tämän vaiheen viimeisessä osassa PC: n (ohjelmalaskurin) kasvattamiseen, jonon lukuosoittimen aikaistamiseen ja jonossa käytettävissä olevien tavujen määrän vähentämiseen.

alustusosion jälkeen nähdään keskeytysprosessointi-osio. Se on vastuussa vireillä olevien keskeytysten havaitsemisesta ja valmistelee suorittimen sen mukaisesti. Kerron tästä seuraavassa jaksossa.

todellinen ohjeen dekoodauslohko tarkistaa, onko pienitehoinen tila ei ole aktiivinen ja onko vianetsintätila pois päältä (OCDCR.DBGMODE=0). Tai virheenkorjaustilassa annettiin yksivaiheinen virheenkorjauskomento (OCDCR.DBGMODE=1 ja OCD.SINGLE_STEP=1). Sitten se tarkistaa käytettävissä tavuja jonossa ja etenee dekoodaus.

jotkin ohjeet (enimmäkseen yksiosaiset) valmistuvat CPU_DECOD-tilassa, kun taas toiset tarvitsevat useita tiloja, kunnes ne ovat täysin valmiit.

huomaa, että jotkut ohjeet dekoodaus voi käyttää useita toimintoja ja menettelyjä kirjoitettu erityisesti FPz8:

- DATAWRITE – tämä menettely valmistelee bussit kirjoitusoperaatiota varten. Se valitsee, onko kohde sisäinen SFR, ulkoinen SFR, tai käyttäjän RAM sijainti.

- DATAREADI – tämä on datawriitin käänteisfunktio. Sitä käytetään lähdeosoitteen lukemiseen ja valitsee automaattisesti, onko kyseessä sisäinen SFR, ulkoinen SFR vai käyttäjän RAM-sijainti.

- CONDITIONCODE – käytetään ehdollisissa ohjeissa (kuten JR ja JP). Se ottaa neljän bitin kuntokoodin, testaa sen ja palauttaa tuloksen.

- ADDRESSER4, ADDRESSER8 ja ADDRESSER12 – nämä funktiot palauttavat 12-bittisen osoitteen neli-, kahdeksan-tai 12-bittisestä lähteestä. He käyttävät RP-rekisterin sisältöä luodakseen lopullisen 12-bittisen osoitteen. ADDRESSER8 ja ADDRESSER12 myös tarkistaa mahdolliset karannut osoitetila.

- ADDER16 – tämä on 16-bittinen address offset-laskenta. Se vie kahdeksanbittisen allekirjoitetun operandin, sign laajentaa sitä, lisää sen 16-bittiseen osoitteeseen ja palauttaa tuloksen.

- ALU ja LU2-näitä käsiteltiin aiemmin, ja ne suorittavat useimmat aritmeettiset ja logiikkaoperaatiot.

keskeytä käsittely

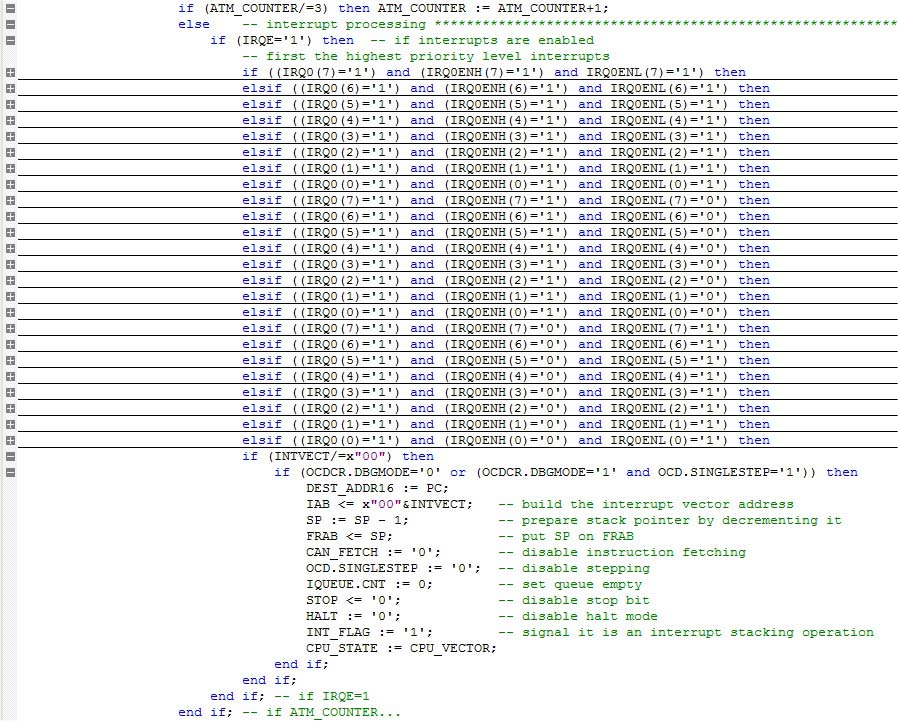

kuten aiemmin sanoin, eZ8: ssa on vektoroitu keskeytysohjain, jolla on ohjelmoitava prioriteetti. Aluksi ajattelin, ettei tämä osio olisi niin vaikea, koska keskeytykset eivät ole iso juttu. No, kun aloin selvittää, miten tehdä kaikki tarvittavat tehtävät(tallentaminen yhteydessä, vectoring, hallinta prioriteetit, jne.), Tajusin, että se olisi vaikeampaa kuin luulin. Parin tunnin kuluttua keksin nykyisen mallin.

FPz8: n keskeytysjärjestelmä päätyi yksinkertaiseksi. Siinä on kahdeksan tuloa (INT0-INT7); maailmanlaajuinen keskeytys käytössä (IRQE-bitti sijaitsee IRQCTL-rekisterissä); kaksi rekisteriä prioriteettiasetukselle (IRQ0ENH ja IRQ0ENL); ja yksi keskeytysrekisteri (IRQ0). Suunnittelussa käytetään sisäkkäistä IF-ketjua,joka luo vektoriosoitteen havaittuaan keskeytystapahtuman, joka koskee keskeytystapahtumaa.

Kuvassa 5 on tiivistetty näkymä keskeytysjärjestelmästä. Huomaa, että on ensimmäinen IF-lauseke symbolilla ATM_COUNTER. Tämä on yksinkertainen laskuri, jota ATM-ohje käyttää (se poistaa keskeytykset kolmen käskysyklin ajaksi, mikä mahdollistaa atomioperaatiot).

kuva 5. FPz8 keskeytysjärjestelmä.

viimeinen huomautus keskeytyksistä: Keskeytyslippurekisteri (IRQ0) – näytteet keskeyttävät syötöt järjestelmän kellon jokaisella nousevalla reunalla. On myös kaksi puskurimuuttujaa (IRQ0_LATCH ja OLD_IRQ0), jotka tallentavat lippujen nykyisen ja viimeisen tilan. Tämä mahdollistaa keskeytysreunan tunnistuksen ja synkronoi myös ulkoiset tulot sisäiseen kelloon (FPGAs eivät toimi hyvin asynkronisten sisäisten signaalien kanssa).

on-Chip Debugger

tämä on luultavasti tämän pehmopornon siistein ominaisuus, koska se mahdollistaa kaupallisen integroidun kehitysympäristön (IDE; kuten Zilogin ZDS-II) kommunikoimaan, ohjelmoimaan ja vianetsintäohjelmistoon, joka toimii fpz8: lla. On-chip debugger (OCD) koostuu UART kanssa autobaud ominaisuus ja komentoprosessori liitetty siihen. UART suorittaa sarjaliikennettä isäntätietokoneen kanssa ja toimittaa komentoja ja tietoja vianetsintätilakoneelle, joka käsittelee vianetsintäkomentoja (vianetsintäkomentojen käsittely FSM sijaitsee CPU_DECOD-tilassa).

kuva 6. On-chip debugger UART (huomaa dbg_rx synkronoija).

OCD-suunnitteluni toteuttaa lähes kaikki todellisessa laitteistossa käytettävissä olevat komennot, lukuun ottamatta niitä, jotka liittyvät datamuistiin (debug-komennot 0x0C ja 0x0d); read runtime counter (0x3); ja read program memory CRC (0x0e).

yksi asia, jonka haluan korostaa, on oltava varovainen, kun käsitellään asynkronisia signaaleja FPGAs: n sisällä. Minun ensimmäinen muotoilu ei huomioon, että käsitellessään dbg_rx tulosignaalin. Tulos oli aivan outo. Suunnitteluni oli toiminut simulaatiossa moitteettomasti. Latasin sen FPGA ja alkoi pelata noin debug serial interface käyttämällä sarjapääte (minun FPGA aluksella on sisäänrakennettu serial-USB muunnin).

yllätyksekseni, vaikka suurimman osan ajasta pystyin lähettämään komentoja ja vastaanottamaan odotetut tulokset, joskus suunnittelu yksinkertaisesti jähmettyi ja lakkasi vastaamasta. Pehmeä nollaus saisi asiat toimimaan, mutta se kiehtoi minua. Mitä tapahtui?

monien testien ja jonkin verran Googlettamisen jälkeen keksin, että se liittyi mahdollisesti sarjatulosignaalin asynkronisiin reunoihin. Sitten mukana ryöppy salpa synkronoida signaalin minun sisäinen kello ja kaikki ongelmat olivat poissa! Tämä on vaikea tapa oppia, että sinun täytyy aina synkronoida ulkoisia signaaleja ennen syöttämällä niitä monimutkaiseen logiikkaan!

minun on sanottava, että vianetsintä ja vianetsintäkoodin jalostaminen oli vaikein osa tätä projektia; lähinnä siksi, että se on vuorovaikutuksessa kaikkien muiden alijärjestelmien kanssa, mukaan lukien linja-autot, dekooderi ja opetusjono.

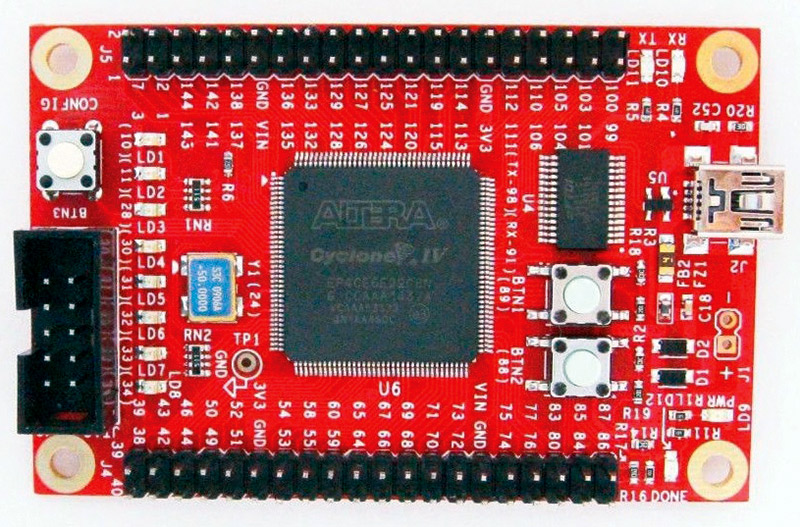

syntetisointi ja testaus

kun se oli täysin koottu (käytin Quartus II V9.1 sp2: ta), fpz8-ytimeen käytettiin 4 900 logiikkaelementtiä, 523 rekisteriä, 147 456 bittiä sirumuistia ja yksi upotettu yhdeksän bitin kerroin. FPz8 käyttää kaiken kaikkiaan 80 prosenttia EP4CE6: n käytettävissä olevista resursseista. Vaikka tämä on paljon, oheislaitteille on vielä saatavilla noin 1200 logiikkaelementtiä (yksinkertainen 16-bittinen ajastimeni lisää noin 120 logiikkaelementtiä ja 61 rekisteriä). Se sopii jopa pienimpään Cyclone IV FPGA-EP4CE6 – joka on asennettu edullinen mini aluksella käytin tässä (kuva 7).

kuva 7. Altera Cyclone IV EP4CE6 mini board.

minilevyn ominaisuudet (yhdessä EP4CE6-laitteen kanssa): EPCS4-sarjakokoonpanomuisti (asennettu alareunaan); FTDI-sarja-USB-muunnin-siru sekä 50 MHz: n kideoskillaattorimoduuli; joitakin painikkeita; LEDejä; ja pin-otsikoita FPGA-nastoihin pääsemiseksi. Integroitua USB-Blasteria (FPGA-ohjelmointiin) ei ole, mutta ostamani paketti sisälsi myös ulkoisen ohjelmoinnin donglen.

mitä reaalimaailman testeihin tulee, On sanomattakin selvää, ettei fpz8 toiminut ensimmäisellä kerralla! Pohdittuani vähän ja luettuani kääntäjän ulostuloviestejä, tajusin, että se oli luultavasti ajoitusongelma. Tämä on hyvin yleinen ongelma suunniteltaessa ohjelmoitavalla logiikalla, mutta koska tämä oli toinen FPGA-suunnitteluni koskaan, en kiinnittänyt siihen tarpeeksi huomiota.

tarkistaessani ajoitusanalyysiviestejä saatoin nähdä varoituksen, että maksimikellon pitäisi olla noin 24 MHz. Aluksi yritin käyttää jakaja-by-2 Tuottaa 25 MHz CPU kello, mutta se ei ollut luotettava. Sitten käytin jakaja-by-3. Kaikki alkoi toimia täydellisesti!

siksi FPz8 toimii tällä hetkellä taajuudella 16,666 MHz. On mahdollista saavuttaa suurempia nopeuksia käyttämällä yhtä sisäistä PLL: ää pääkellon kertomiseen/jakamiseen, jotta tuloksena oleva kello olisi pienempi kuin 24 MHz, mutta suurempi kuin 16,666 MHz.

ohjelmointi ja vianetsintä

FPz8: n käyttäminen on hyvin yksinkertaista ja suoraviivaista. Kun suunnittelu on ladattu FPGA: lle, suoritin alkaa suorittaa mitä tahansa muistiin ladattua ohjelmaa. Voit toimittaa hex-tiedoston ja käyttää MegaWizard Plug-In Manager muuttaa ohjelman muistin alustustiedoston. Näin sovelluskoodi käynnistyy reset-signaalin jälkeen.

voit käyttää Zilog ZDS-II IDE: tä Assembly-tai C-koodin kirjoittamiseen ja tarvittavien hex-tiedostojen luomiseen (valitsen yleensä z8f1622: n kohdelaitteekseni, sillä siinä on myös 2 KB RAM-muistia ja 16 KB ohjelmamuistia). Sirullisen debuggerin ansiosta on myös mahdollista käyttää ZDS-II IDE: tä koodin lataamiseen fpz8: aan sarjajäljennysyhteyden (USB, meidän tapauksessamme) avulla.

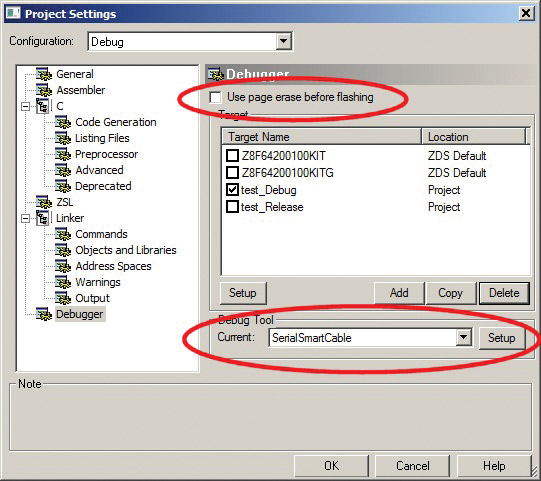

ennen yhdistämistä varmista, että debuggerin asetukset ovat samat kuin kuvassa 8. Poista merkintä” käytä page erase ennen vilkkua ”vaihtoehto, ja valitse” SerialSmartCable ” kuin nykyinen debug työkalu. Älä unohda myös tarkistaa, onko FTDI: n virtuaalinen COM-portti valittu oikein vianetsintäporttiksi (käytä Määrityspainiketta). Voit myös asettaa halutun viestintänopeuden; 115,200 bps toimii minulle erittäin hyvin.

kuva 8. Vianetsintäasetukset.

huomaa, että kun kytket FPz8: aan, ZDS-II IDE näyttää varoitusviestin, jossa kerrotaan, että kohdelaite ei ole sama kuin projekti. Niin käy, koska en ottanut käyttöön joitain ID-muistialueita. Jätä varoitus huomiotta ja jatka vianetsintäistuntoa.

kun koodi on ladattu onnistuneesti, voit käynnistää sovelluksen (GO-painike), askelohjeet, tarkastaa tai muokata rekistereitä, asettaa keskeytyspisteitä jne. Kuten minkä tahansa muun hyvän debuggerin kohdalla, voit esimerkiksi valita PAOUT-rekisterin (PORTS group) ja jopa muuttaa PAOUT-järjestelmään liitettyjen LEDien tilaa.

joitakin yksinkertaisia C-koodiesimerkkejä löytyy latauksista.

muista, että fpz8: ssa on haihtuva ohjelmamuisti. Näin, Mikä tahansa ohjelma ladattu siihen menetetään, kun FPGA on kytketty pois päältä.

loppuunsaattaminen

tämä projekti kesti pari viikkoa, mutta mikrokontrolleriytimen tutkimus ja suunnittelu oli ilahduttavaa.

toivon, että tämä projekti voi olla hyödyllinen kaikille, jotka haluavat oppia tietojenkäsittelyn perusasioista, mikrokontrollereista, sulautetusta ohjelmoinnista ja/tai VHDL: stä. Uskon, että — jos pariksi edullinen FPGA aluksella-FPz8 voi tarjota fantastinen oppimisen (ja opetus) työkalu. Pitäkää hauskaa! NV

CEFET-PR:

www.utfpr.edu.br

ScTec:

www.sctec.com.br

HCS08 Unleashed:

https://www.amazon.com/HCS08-Unleashed-Designers-Guide-Microcontrollers/dp/1419685929

Zilog eZ8 CPU Manual (UM0128):

www.zilog.com/docs/UM0128.pdf

Zilog Z8F64xx Product Specification (PS0199):

www.zilog.com/docs/z8encore/PS0199.pdf

Zilog ZDS II IDE User Manual (UM0130):

www.zilog.com/docs/devtools/UM0130.pdf

Zilog ZDS-II Software Download:

https://www.zilog.com/index.php?option=com_zcm&task=view&soft_id=7&Itemid=74

Zilog Microcontroller Product Line:

http://zilog.com/index.php?option=com_product&task=product&businessLine=1&id=2&parent_id=2&Itemid=56

Project Files available at:

https://github.com/fabiopjve/VHDL/tree/master/FPz8

FPz8 at Opencores.org:

http://opencores.org/project,fpz8