ez a cikk a mikrokontroller mag tervezésének megismerésére összpontosít, és csak oktatási célokra szolgál. Kérjük, látogasson el www.zilog.com ellenőrizze a gyártó termékcsaládját, hogy kiválasszon egy mikrokontrollert, amely megfelel a projekt igényeinek (a nyolc bites Z8 Encores-ből! az eZ80 pedig elismeri a 32 bites ARM Cortex-M3 alapú ZNEO32-et! amely magában foglalja a fejlett motorvezérlő képességeket).

szerelmi viszonyom a mikrovezérlőkkel és mikroprocesszorokkal 1988-ban kezdődött, amikor a CEFET-PR-nél (egy négyéves Brazil Középiskola/Műszaki Iskola és egyetem Curitibában) MŰSZAKI diplomát szereztem. Az alapok elsajátításával kezdtem, miközben a klasszikus Zilog Z-80-at fedeztem fel (1a ábra).

1A. ábra: a Zilog Z-80A (a Wikimedia Commons jóvoltából).

gyors előre a programozási karrieren keresztül, amely magában foglalta a mikrokontroller programozásáról szóló könyvek szerzését (lásd források), egy kis tervezőház (ScTec) indítását és egy posztgraduális program befejezését a CEFET-SC-ben (egy másik brazil egyetem, Florianopolis). Ez 2008-ban volt, amikor több kapcsolatom volt a programozható logikával és a VHDL-lel, és a kíváncsiságom tetőzött. Évekkel később, 2016-ban találtam egy nagyon megfizethető FPGA (Field-Programmable Gate Array) készletet, és úgy döntöttem, hogy adok neki egy esélyt, és elkezdtem többet megtudni az FPGA technológiáról.

mi lenne jobb, mint egy softcore tervezése, hogy többet tudjon meg a VHDL-ről (vhsic hardware description language), az FPGA-król és a mikroprocesszoros magokról? Végül egy modern Z-80 rokont választottam: a Zilog Z8 Encore-t! (más néven: eZ8; 1b. ábra).

ábra 1b. Zilog eZ8.

ez egy nyolc bites mikrokontroller mag egy egyszerű-mégis erőteljes — utasításkészlettel és egy nagyon szép on — chip hibakeresővel. A könnyű IDE (integrated development environment) és a szabad ANSI C fordító, Ez egy kiváló projekt tanulni (és tanítani) a beágyazott rendszerek.

mielőtt belemerülnénk a magműködés, a VHDL és az FPGA mélységeibe, vessünk egy pillantást a Zilog Z8 Encore-ra! jellemzők.

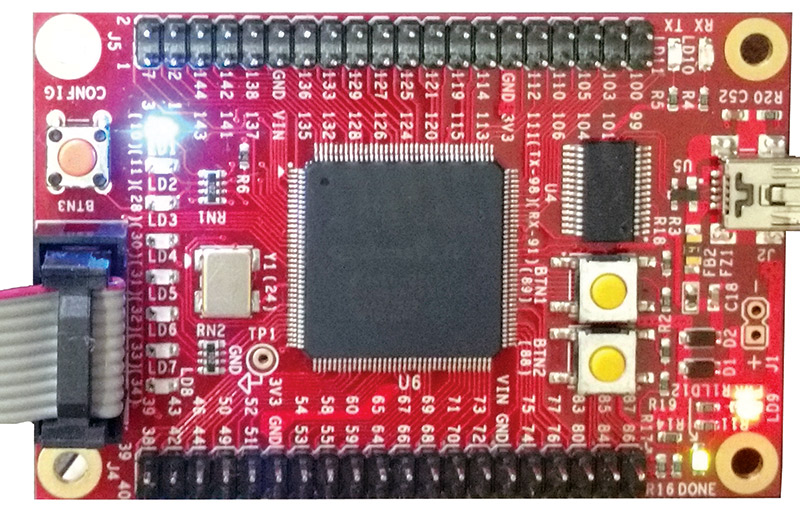

ábra 1C. FPz8 egy FPGA.

Zilog Z8 Ráadás!

az eZ8 egy nyolc bites mikrovezérlő család, amely a Zilog sikeres Z8 családján és a nagy Z-80 örökségen alapul. Tartalmaz egy Harvard CISC gépet, amely legfeljebb 4096 bájt RAM-ot (fájlregiszter és speciális funkcióregiszterek területe), legfeljebb 64 KB programmemóriát (általában Flash memóriát) és legfeljebb 64 KB adatmemóriát (RAM) tartalmaz. Az eZ8 mag tartalmaz egy programozható prioritású vektoros megszakításvezérlőt és egy chip-alapú hibakeresőt, amely aszinkron soros kommunikációval kommunikál a gazdaszámítógéppel. Ezek a mikrokontrollerek nagyon szép perifériás készletekkel vannak ellátva, a sokoldalú 16 bites időzítőktől a motorvezérlő időzítőkig, a több UART-tól (IrDA ready) az USB-eszközökig, és még sok más (látogatás www.zilog.com a teljes termékcsalád ellenőrzése).

az eZ8 programozási modell egyik fő jellemzője a rögzített akkumulátor hiánya. Ehelyett a 4096 lehetséges RAM-cím bármelyike akkumulátorként működhet. A CPU a fő RAM — ját (a file and SFRs — special function registers-area) a CPU regiszterek nagy készleteként kezeli. Ennek elérése érdekében a RAM-ot regisztercsoportokra osztják (256 csoport van, egyenként 16 működő regiszterrel). Az utasítás általában egyetlen működő regisztercsoporton belül működik, amelyet egy RP (regisztermutató) nevű SFR választ ki. Vegye figyelembe, hogy az összes SFR a RAM utolsó oldalán található (0xf00-tól 0xFFF-ig terjedő címek).

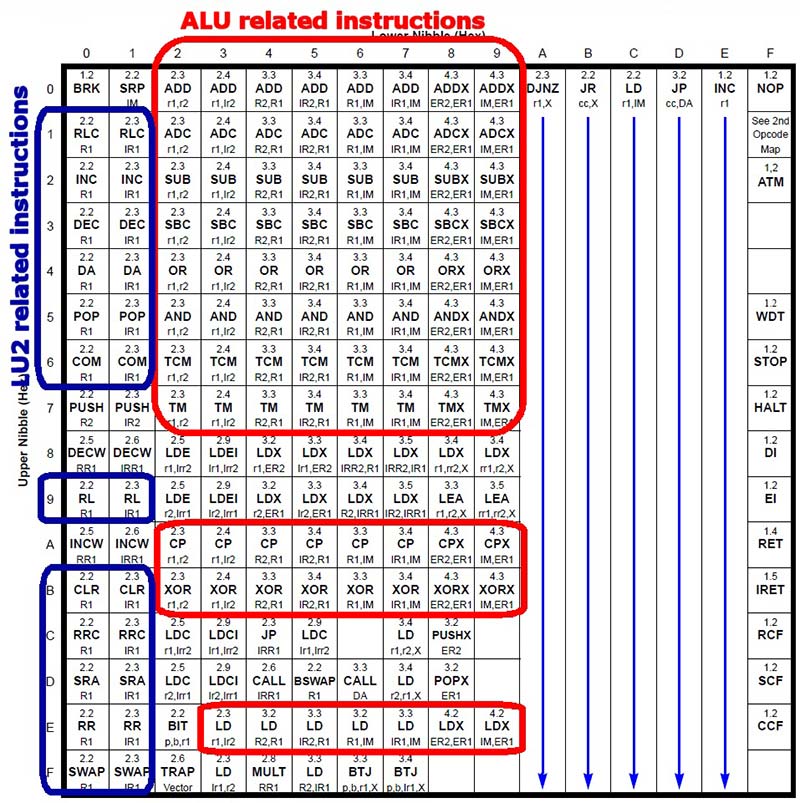

az utasításkészletet illetően 83 különböző utasítás van felosztva két opcode oldalra. Ez magában foglalja a szokásos utasításokat az alapvető műveletekhez, mint például az összeadás, kivonás, logikai műveletek, Adatkezelési utasítások, shifting utasítások, Change-of-flow utasítások, néhány 16 bites utasítás, bit tesztelés és manipuláció, 8×8 szorzás stb.

a program memóriaterülete úgy van megszervezve, hogy az első címek speciális célokra legyenek szentelve. A 0x0000 és 0x0001 címek a konfigurációs opcióknak vannak szentelve; a 0x0002 és 0x0003 címek tárolják a reset vektort; és így tovább. Táblázat 1 mutatja program memória szervezet.

| 0x0000 | Option bytes |

| 0x0002 | Reset vector |

| 0x0004 | WDT vector |

| 0x0006 | Illegal instruction vector |

| 0x0008 to 0x0037 | Interrupt vectors |

| 0x0038 to 0xFFFF | User program memory area |

TABLE 1. Simplified program memory organization.

néhány eszköz tartalmaz egy második adatteret is (legfeljebb 65 536 cím), amelyhez csak LDE/LDEI utasításokkal lehet hozzáférni. Ez a terület kevésbé használt adatok tárolására használható (mivel az olvasás/írás lassabb, mint a RAM/SFR terület).

FPz8

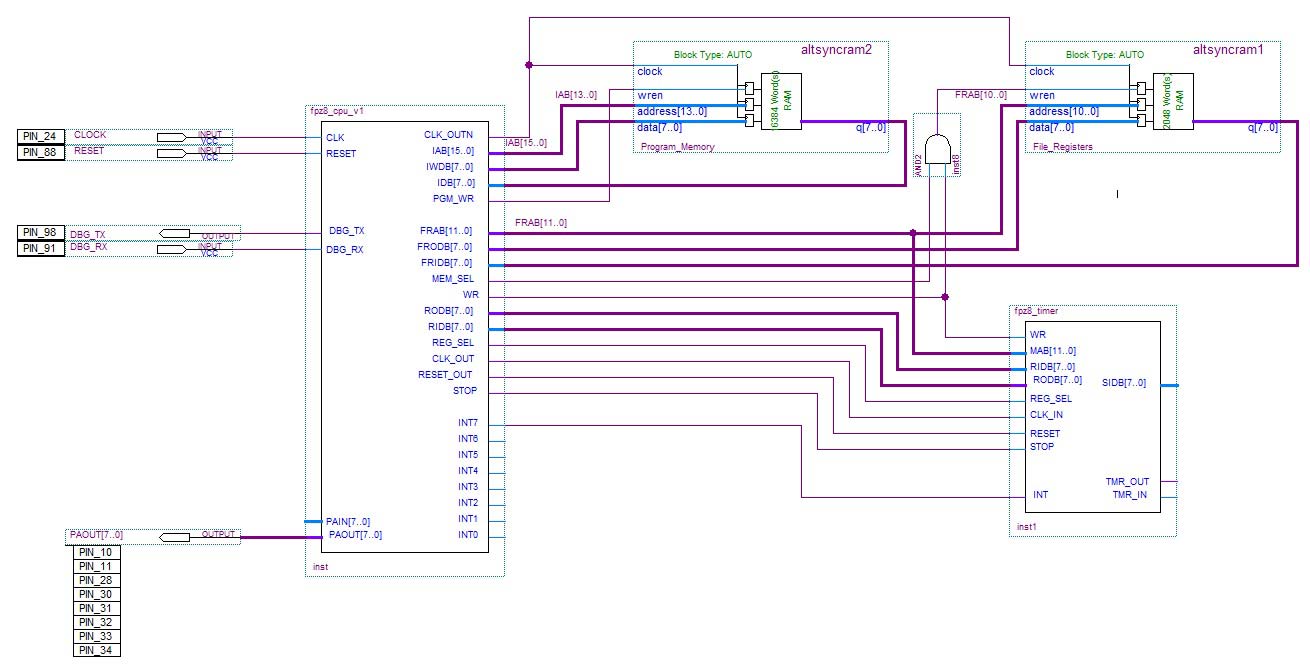

az FPz8 első megvalósítása nagyon konzervatív és vezetékes tervezési megközelítést alkalmaz, két fő buszral: az egyik a programmemóriához, a másik a regisztermemóriához. Mivel úgy döntöttem, hogy nem tartalmaz adatmemória területet, az LDE/LDEI utasításokat nem hajtják végre.

a programmemória-buszok tartalmaznak egy 16 bites utasításcímsínt (IAB), egy nyolc bites utasítás-adatbuszt (IDB a programmemóriából származó adatok olvasására), egy nyolc bites utasítás-írási adatbuszt (IWDB az adatok programmemóriába történő írására), valamint egy PGM_WR jelet, amely a programmemóriába történő írást vezérli. Az FPz8 16 384 bájt programmemóriát tartalmaz szinkron blokk RAM használatával (ami azt jelenti, hogy a program memóriatartalma elvész, amikor az eszköz le van kapcsolva).

az öt regiszterterület-busz háromból áll a fájlregiszter-területhez (felhasználói RAM), további kettő pedig a speciális funkcióregiszterekhez. Van egy fő 12 bites fájlregiszter címsín (FRAB), egy nyolc bites fájlregiszter bemeneti adatbusz (FRIDB), egy nyolc bites fájlregiszter kimeneti adatbusz (FRODB), egy nyolc bites regiszter bemeneti adatbusz (RIDB), végül egy nyolc bites regiszter kimeneti adatbusz (RODB) az SFRs-be történő íráshoz. Az FPz8 2048 bájt felhasználói RAM memóriát tartalmaz szinkron blokk RAM használatával.

a 2. ábra az FPz8 blokkdiagramját mutatja; láthatjuk a CPU-t, két memóriaegységet (az egyik a program tárolására, a másik az adattárolásra), valamint egy külső időzítő modult.

2. ábra. FPz8 blokkdiagram.

vegye figyelembe, hogy nem használok kétirányú buszokat a projektben lévő összeköttetésekhez. Az egyirányú buszok használata egyszerűbb, bár kevésbé helytakarékosak.

az FPz8 VHDL leírása nagy és kissé összetett, ezért a működését néhány modulra osztom, hogy megkönnyítsem a megértést:

- utasítás sorakozó motor

- utasítás dekódolás

- megszakítás feldolgozás

- hibakereső

utasítás sorakozó Motor

az utasítások lekérése minden CPU elsődleges feladata. Az FPz8 Harvard architektúrája lehetővé teszi az egyidejű letöltést és adathozzáférést (az utasítások és adatok külön buszainak köszönhetően). Ez azt jelenti, hogy a CPU új utasítást tud letölteni, miközben egy másik olvas vagy ír az adatmemóriába.

az eZ8 változó hosszúságú utasításszóval rendelkezik (az utasítás hossza egy bájttól öt bájtig változik); egyes utasítások hosszúak, de gyorsabban futnak, mint mások. Így a BRK utasítás hossza egy bájt, és két ciklusban fut, míg az LDX IM, ER1 négy bájt hosszú és két órajelciklusban fut.

Szóval, hogyan tudjuk sikeresen dekódolni ezeket az utasításokat? Utasítássorral; vagyis egy olyan mechanizmussal, amely bájtokat tölt le a program memóriájából, és tárolja őket egy nyolc bájtos tömbbe:

if (CAN_FETCH=’1′), majd

if (IQUEUE.FETCH_STATE=F_ADDR), majd

FETCH_ADDR := PC;

IAB <= PC;

IQUEUE.WRPOS: = 0;

IQUEUE.RDPOS: = 0;

IQUEUE.CNT := 0;

IQUEUE.FETCH_STATE: = F_READ;

else

if (IQUEUE.FULL = ‘0’), majd

IQUEUE.SOR (IQUEUE.WRPOS): = IDB;

FETCH_ADDR := FETCH_ADDR + 1;

IAB <= FETCH_ADDR;

IQUEUE.WRPOS: = IQUEUE.WRPOS + 1;

IQUEUE.CNT: = IQUEUE.CNT + 1;

vége, ha;

vége, ha;

vége, ha;

ha (IQUEUE.CNT=7), majd IQUEUE.Teljes:= ‘1’; else IQUEUE.FULL: = ‘0’;

vége if;

lista 1. Utasítás sor motor.

a letöltést egy fő enable jel (CAN_FETCH) vezérli, amely bizonyos speciális esetekben letiltható (megszakítási feldolgozás, LDC/LDCI utasítások vagy hibakereső hozzáférés). Van egy struktúra (IQUEUE), amely több belső paramétert tárol (lekérési állapot, olvasási és írási mutatók, maga a sor tömb, számláló és teljes indikátor).

a várólista számláló (CNT) a várólistában használható (olvasható) bájtok számának azonosítására szolgál. A dekóder szakasz ezt a számot használja annak ellenőrzésére, hogy az utasításhoz szükséges bájtok száma már elérhető-e a sorban.

utasítás dekódolás

itt történik a tényleges varázslat. Az utasításdekódoló beolvassa az opkódokat az utasítássorból, és lefordítja azokat a megfelelő műveletekre.

Utasításdekóder tervezés az utasítások és címzési módok közötti kapcsolat feltárásával kezdődött. Első látásra könnyen belátható, hogy egyes utasítások (3.ábra) oszlop szerint vannak csoportosítva (DJNZ, JR cc,X, LD r1,IM, JP cc,DA És INC R1). Az INC R1 utasítás dekódolása egyszerű: ezeken az egybájtos utasításokon a magas nibble megadja a forrás/cél regisztert, az alsó nibble pedig magát az utasítást (0xE).

3. ábra. Opkódok csoportok szerint.

a legtöbb utasítás néhány alapvető szabály szerint osztályozható:

- az oszlopok (az opkód alsó harapása) általában megadják a címzési módot: A 0X9 oszlop utasításai például többnyire az IM, ER1 címzési módot használják, és négy bájt hosszúak (a második bájt az azonnali operandus, a két utolsó bájt pedig a cél kiterjesztett címe).

- a sorok (az opkód magasabb harapása) általában megadnak egy műveletet: a 0x0 sor utasításai többnyire összeadási műveletek; a 0x2 sor utasításai többnyire kivonási műveletek stb.

ha megnézzük a 0x1 Sort, láthatjuk, hogy a 0x0 és 0x1 oszlopok RLC utasítások, a 0x2-től 0x9-ig terjedő oszlopok pedig ADC utasítások. Tehát megtervezhetünk egy ALU-t, amely bemenetként egy nibble-t vesz fel (az opkód magasabb nibble-je), és ennek megfelelően dekódolja. Bár ez a 0x2-0x9 oszlopoknál működne, az első két oszlophoz más megközelítésre lenne szükségünk.

ezért végül két egységet írtam: egy ALU-t, amely a legtöbb aritmetikai és logikai utasításra összpontosít; és egy második egységet (logikai egység 2, vagy LU2), amely a 0x0 és 0x1 oszlopokban bemutatott egyéb műveleteket hajtja végre (nem minden, az oszlopokon látható műveletet hajt végre LU2). Mind az ALU, mind az LU2 működési kódjait úgy választottuk meg, hogy megfeleljenek a 3.ábrán látható opcode soroknak.

további fontos részlet, hogy az ugyanazon oszlopon és csoporton belüli összes utasítás bájtban azonos méretű, így ugyanabban a dekóder szakaszban dekódolható.

a dekóder kialakítása egy nagy véges állapotú gépet (FSM) használ, amely minden egyes órajelnél előrehalad. Minden utasítás a CPU_DECOD stat-ban kezdődik. Ez az, ahol a dekóder ténylegesen dekódolja az opkódokat, előkészíti a buszokat és a belső támogató jeleket, és lépéseket tesz más végrehajtási állapotokra. Ezen állapotok közül kettőt széles körben használnak sok utasítás: CPU_OMA és CPU_OMA2. Meg tudja tippelni, miért? Ha azt mondta, mert kapcsolatban állnak az ALU-val és az LU2-vel, akkor teljesen igaza van!

az OMA a One Memory Access rövidítése, és az összes ALU-val kapcsolatos utasítás (ADD, ADC, ADDX, ADCX, SUB, SBC, SUBX, SBCX, OR, ORX, ANDX, XOR, XORX, CP, CPC, TCMX, TM, TMX, valamint az LD és LDX egyes változatai) Utolsó állapota. Másrészt a CPU_OMA2 az összes LU2-vel kapcsolatos utasítás (RLC, INC, DEC, DA, COM, RL, CLR, RRC, SRA, SRL, RR és SWAP) Utolsó állapota.

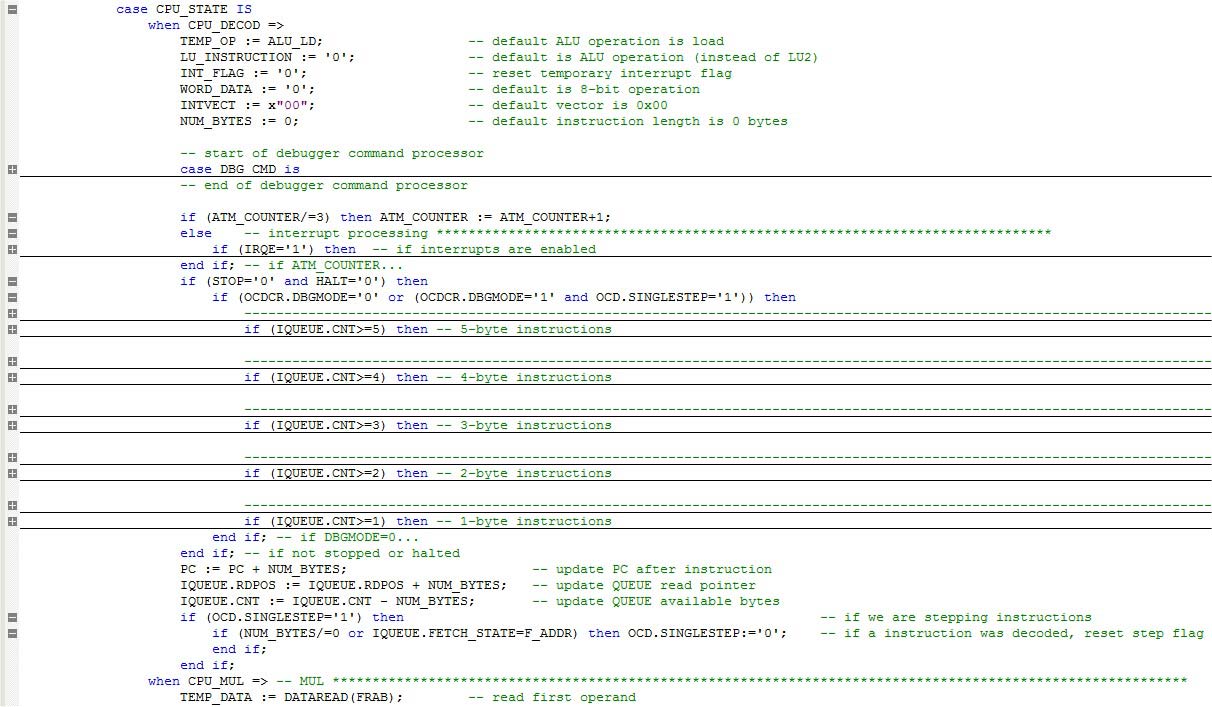

most vessünk egy pillantást a CPU_DECOD állapotba. Lásd a 4. ábrát.

4. ábra. CPU_DECOD állapot.

a CPU_DECOD állapotban láthatjuk, hogy sok akció zajlik. Kezdetben néhány ideiglenes változót inicializálnak egy alapértelmezett feltételre. Vegye figyelembe, hogy a NUM_BYTES nagyon fontos, mivel szabályozza, hogy hány bájtot fogyasztott az utasítás dekóder. Ennek értékét a szakasz utolsó részében használják a PC (programszámláló) növelésére, a várólista olvasási mutatójának előmozdítására, valamint a várólistában elérhető bájtok számának csökkentésére.

az inicializálási szakasz után láthatjuk a megszakítás feldolgozás részt. Felelős a függőben lévő megszakítások észleléséért, és ennek megfelelően előkészíti a CPU-t. Ezt a következő részben ismertetem.

a tényleges utasítás dekódoló blokk ellenőrzi, hogy az alacsony fogyasztású üzemmód nem aktív-e, valamint hogy a hibakereső mód ki van-e kapcsolva (OCDCR.DBGMODE=0). Vagy hibakeresési módban egylépéses hibakeresési parancsot adtak ki (OCDCR.DBGMODE=1 és OCD.SINGLE_STEP=1). Ezután ellenőrzi a rendelkezésre álló bájtokat a sorban, és folytatja a dekódolást.

egyes utasítások (főleg az egybájtos utasítások) a CPU_DECOD állapotban vannak kitöltve, míg másoknak több állapotra van szükségük, amíg teljesen be nem fejeződnek.

vegye figyelembe, hogy egyes utasítások dekódolása számos funkciót és eljárást használhat, amelyeket kifejezetten az FPz8-hoz írtak:

- DATAWRITE-ez az eljárás előkészíti a buszokat egy írási művelethez. Kiválasztja, hogy a cél egy belső SFR, egy külső SFR vagy egy felhasználói RAM hely.

- DATAREAD — ez a DATAWRITE kölcsönös funkciója. A forráscím olvasására szolgál, és automatikusan kiválasztja, hogy ez egy belső SFR, egy külső SFR vagy egy felhasználói RAM hely.

- CONDITIONCODE — feltételes utasításokhoz (például JR és JP) használatos. Egy négy bites feltételkódot vesz igénybe, teszteli, és visszaadja az eredményt.

- ADDRESSER4, ADDRESSER8 és ADDRESSER12 — ezek a függvények 12 bites címet adnak vissza négy, nyolc vagy 12 bites forrásból. Az RP regiszter tartalmát használják a végső 12 bites cím előállításához. ADDRESSER8 és ADDRESSER12 is ellenőrzi az esetleges megszökött címzési mód.

- ADDER16 — ez egy 16 bites adder cím eltolás számítás. Egy nyolc bites aláírt operandust vesz igénybe, a sign kiterjeszti, hozzáadja a 16 bites címhez, és visszaadja az eredményt.

- ALU és LU2 — ezeket korábban tárgyaltuk, és a legtöbb aritmetikai és logikai műveletet elvégzik.

megszakítás feldolgozás

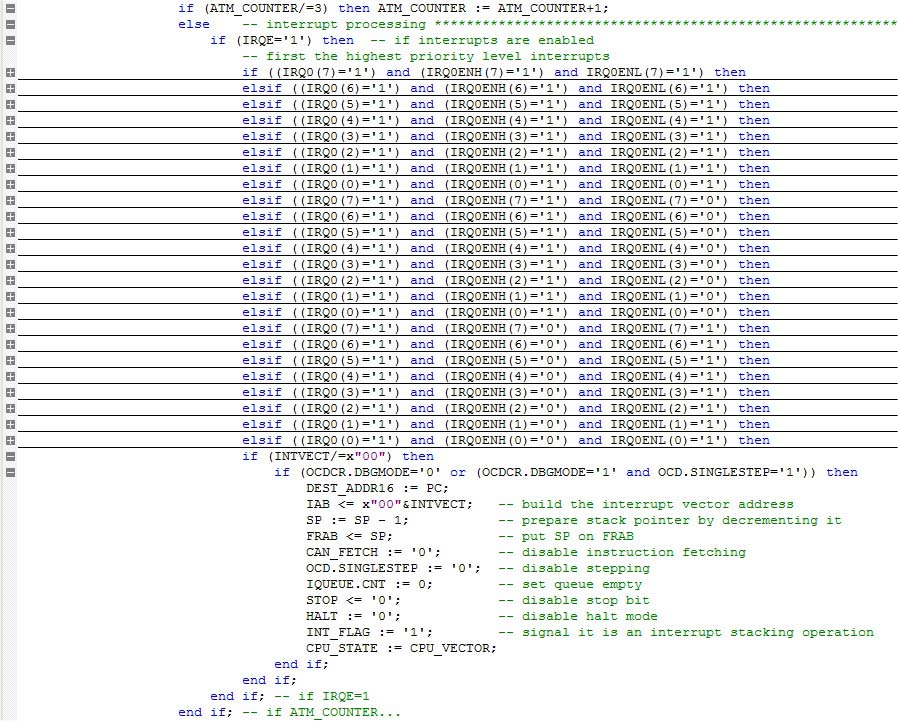

mint korábban mondtam, az eZ8-nak van egy vektoros megszakításvezérlője programozható prioritással. Először azt hittem, hogy ez a szakasz nem lesz olyan nehéz, mert a megszakítások nem nagy ügy, igaz? Nos, amikor elkezdtem kitalálni, hogyan kell elvégezni az összes szükséges feladatot (kontextus mentése, vektorálás, prioritások kezelése stb.), Rájöttem, hogy keményebb lesz, mint gondoltam. Néhány óra múlva kitaláltam a jelenlegi tervet.

az FPz8 megszakítási rendszere végül egyszerű volt. Nyolc bemenete van (INT0-INT7); egy globális megszakítási engedélyezés (IRQE bit az IRQCTL regiszterben található); két regiszter a prioritás beállításához (IRQ0ENH és IRQ0ENL); és egy regiszter a megszakítási zászlókhoz (IRQ0). A tervezés egy beágyazott IF láncot használ, amely vektorcímet generál az engedélyezett megszakítással kapcsolatos megszakítási esemény észlelésekor.

az 5.ábra a megszakító rendszer tömörített nézetét mutatja. Megjegyzés: van egy első IF utasítás egy szimbólummal ATM_COUNTER. Ez egy egyszerű számláló, amelyet az ATM utasítás használ (letiltja a megszakításokat három utasításciklusra, lehetővé téve az atomi műveleteket).

5. ábra. FPz8 megszakító rendszer.

egy utolsó megjegyzés a megszakításokkal kapcsolatban: A megszakítási zászló regiszter (IRQ0) minták megszakítják a bemeneteket a rendszer órájának minden emelkedő szélén. Két pufferváltozó is van (IRQ0_LATCH és OLD_IRQ0), amelyek a zászlók aktuális és utolsó állapotát tárolják. Ez lehetővé teszi a megszakítási él észlelését, valamint szinkronizálja a külső bemeneteket a belső órával (az FPGA-k nem működnek jól az aszinkron belső jelekkel).

on-Chip Debugger

ez talán a legmenőbb jellemzője ennek a softcore, mivel lehetővé teszi a kereskedelmi integrált fejlesztői környezet (IDE; mint például a Zilog ZDS-II) az FPz8-on futó szoftverek kommunikálására, programozására és hibakeresésére. Az on-chip debugger (OCD) egy autobaud képességgel rendelkező UART-ból és egy hozzá csatolt parancsprocesszorból áll. Az UART soros kommunikációt hajt végre egy gazdagéppel, és parancsokat és adatokat szállít a hibakereső állapotú géphez, amely feldolgozza a hibakeresési parancsokat (a hibakereső parancsfeldolgozó FSM a CPU_DECOD állapotban található).

6. ábra. On-chip debugger UART (megjegyzés: a dbg_rx szinkronizáló).

az OCD tervezésem szinte az összes parancsot végrehajtja a valódi hardveren, kivéve azokat, amelyek az adatmemóriához kapcsolódnak (0x0c és 0x0d hibakeresési parancsok); az olvasási futásidejű számláló (0x3); és az olvasási programmemória CRC (0x0e).

egy dolgot szeretnék kiemelni, hogy körültekintően kell eljárni az FPGA-Kon belüli aszinkron jelek kezelésekor. Az első tervem ezt nem vette figyelembe a dbg_rx bemeneti jel feldolgozása közben. Az eredmény teljesen furcsa volt. A tervem hibátlanul működött a szimulációban. Letöltöttem egy FPGA-ra, és elkezdtem játszani a debug soros interfésszel egy soros terminál használatával (az FPGA kártyám beépített soros-USB átalakítóval rendelkezik).

meglepetésemre, míg az idő nagy részében sikeresen küldhettem parancsokat és megkaptam a várt eredményeket, néha a tervezés egyszerűen lefagyott és nem válaszolt. A soft reset lehetővé tenné, hogy a dolgok visszatérjenek a megfelelő működéshez, de ez érdekes volt számomra. Mi történt?

sok teszt és némi guglizás után rájöttem, hogy valószínűleg a Soros bemeneti jel aszinkron éleihez kapcsolódik. Ezután mellékeltem egy kaszkádos reteszt, hogy szinkronizáljam a jelet a belső órámhoz, és minden probléma eltűnt! Ez egy kemény módja annak, hogy megtanulják, hogy meg kell mindig szinkronizálni a külső jeleket etetés előtt őket komplex logika!

azt kell mondanom, hogy a hibakereső kód hibakeresése és finomítása volt a projekt legnehezebb része; leginkább azért, mert kölcsönhatásba lép az összes többi alrendszerrel, beleértve a buszokat, a dekódert és az utasítássort.

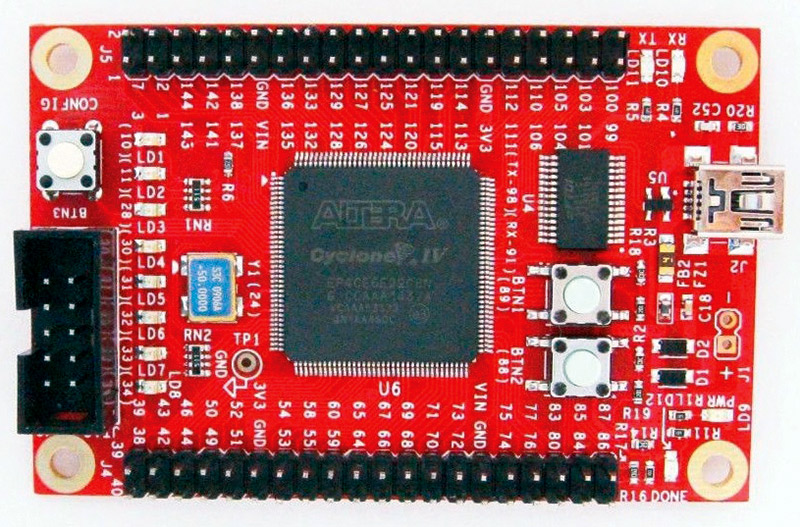

szintetizálása és tesztelése a teljes fordítás után (a Quartus II v9.1 sp2-t használtam) az FPz8 mag 4900 logikai elemet, 523 regisztert, 147 456 bit chipen lévő memóriát és egy beágyazott kilenc bites szorzót használt fel. Összességében az FPz8 az EP4CE6 rendelkezésre álló erőforrásainak 80% – át használja fel. Bár ez sok, még mindig 1200 logikai elem áll rendelkezésre a perifériákhoz (az egyszerű 16 bites időzítőm körülbelül 120 logikai elemet és 61 regisztert tartalmaz). Még a legkisebb Cyclone IV FPGA — ra is elfér-az EP4CE6-ra -, amely az itt használt olcsó mini táblára van felszerelve (7.ábra).

7. ábra. Altera Cyclone IV EP4CE6 mini tábla.

a mini tábla jellemzői (az EP4CE6 eszközzel együtt): EPCS4 soros konfigurációs memória (az alsó oldalra szerelve); egy FTDI soros-USB átalakító chip, valamint egy 50 MHz-es kristály oszcillátor modul; néhány gomb; LED; és pin fejlécek az FPGA csapok eléréséhez. Nincs beépített USB-Blaster (FPGA programozáshoz), de a megvásárolt csomag tartalmazott egy külső programozási dongle-t is.

ami a valós teszteket illeti, mondanom sem kell, hogy az FPz8 nem működött először! Miután egy kicsit elgondolkodtam és elolvastam a fordító kimeneti üzeneteit, rájöttem, hogy valószínűleg időzítési kérdés. Ez egy nagyon gyakori dilemma, amikor programozható logikával tervezek, de mivel ez volt a második FPGA tervezésem, nem fordítottam rá elég figyelmet.

az időzítési elemzési üzenetek ellenőrzése során figyelmeztetést láttam, hogy a maximális órajelnek 24 MHz körül kell lennie. Először megpróbáltam egy 2-es osztót használni egy 25 MHz-es CPU óra létrehozásához, de ez nem volt megbízható. Ezután egy osztót használtam-by-3. Minden tökéletesen kezdett működni!

ezért az FPz8 jelenleg 16,666 MHz-en fut. Nagyobb sebességet lehet elérni az egyik belső PLL használatával a fő óra szorzásához/felosztásához annak érdekében, hogy a kapott óra 24 MHz-nél alacsonyabb, de 16,666 MHz-nél magasabb legyen.

programozás és hibakeresés

az FPz8 használata nagyon egyszerű és egyértelmű. Miután letöltötte a tervet az FPGA-ra, a CPU elkezdi futtatni a memóriába betöltött programokat. Megadhat egy hex fájlt, és a MegaWizard Plug-In Manager segítségével módosíthatja a program memória inicializáló fájlját. Így az alkalmazás kódja egy visszaállítási jelet követően indul el.

használhatja a Zilog ZDS-II IDE-t Assembly vagy C kód írására, és létrehozhatja a szükséges hex fájlokat (általában a z8f1622-et választom céleszközként, mivel 2 KB RAM-mal és 16 KB programmemóriával is rendelkezik). A chipen lévő hibakeresőnek köszönhetően a ZDS-II IDE segítségével soros hibakeresési kapcsolat (esetünkben USB) segítségével is letöltheti a kódot az FPz8-ra.

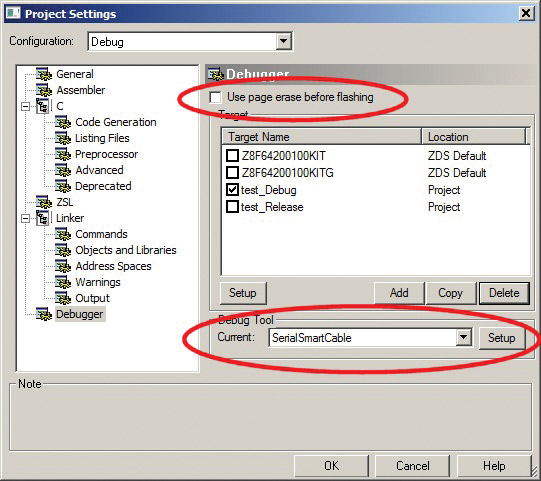

csatlakozás előtt ellenőrizze, hogy a hibakereső beállításai megegyeznek-e a 8.ábrán látható beállításokkal. Törölje a jelölést az “oldal törlése villogás előtt” opcióból, majd válassza a “SerialSmartCable” lehetőséget az aktuális hibakereső eszközként. Ne felejtse el ellenőrizni azt is, hogy az FTDI virtuális COM portja helyesen van-e kiválasztva hibakeresési portként (használja a Beállítás gombot). Beállíthatja a kívánt kommunikációs sebességet is; a 115 200 bps nagyon jól működik nekem.

8. ábra. Hibakereső beállítások.

vegye figyelembe, hogy az FPz8-hoz való csatlakozáskor a ZDS-II IDE figyelmeztető üzenetet jelenít meg, amely tájékoztatja Önt arról, hogy a céleszköz nem ugyanaz, mint a projekt. Ez azért történik, mert nem valósítottam meg néhány ID memória területet. Csak hagyja figyelmen kívül a figyelmeztetést, és folytassa a hibakeresési munkamenetet.

a kód sikeres letöltése után elindíthatja az alkalmazást (GO gomb), lépés utasítások, regiszterek ellenőrzése vagy szerkesztése, töréspontok beállítása stb. Mint minden más jó hibakeresőnél, kiválaszthatja például a PAOUT regisztert (a portok csoport alatt), sőt megváltoztathatja a PAOUT-hoz csatlakoztatott LED-ek állapotát is.

néhány egyszerű C-kód példa megtalálható a letöltésekben.

csak ne feledje, hogy az FPz8 Illékony programmemóriával rendelkezik. Így minden letöltött program elvész, amikor az FPGA le van kapcsolva.

záró

ez a projekt néhány hétig tartott, de kellemes volt a mikrokontroller mag kutatása és tervezése.

remélem, hogy ez a projekt hasznos lehet bárki számára, aki meg akarja tanulni a számítástechnika alapjait, a mikrokontrollereket, a beágyazott programozást és/vagy a VHDL-t. Úgy gondolom — hogy ha egy olcsó FPGA kártyával párosítjuk — az FPz8 fantasztikus tanulási (és tanítási) eszközt nyújthat. Jó szórakozást! NV

CEFET-PR:

www.utfpr.edu.br

ScTec:

www.sctec.com.br

HCS08 elszabadult:

https://www.amazon.com/HCS08-Unleashed-Designers-Guide-Microcontrollers/dp/1419685929

Zilog EZ8 CPU kézikönyv (UM0128):

www.zilog.com/docs/UM0128.pdf

Zilog Z8F64xx Product Specification (PS0199):

www.zilog.com/docs/z8encore/PS0199.pdf

Zilog ZDS II IDE User Manual (UM0130):

www.zilog.com/docs/devtools/UM0130.pdf

Zilog ZDS-II Software Download:

https://www.zilog.com/index.php?option=com_zcm&task=view&soft_id=7&Itemid=74

Zilog Microcontroller Product Line:

http://zilog.com/index.php?option=com_product&task=product&businessLine=1&id=2&parent_id=2&Itemid=56

Project Files available at:

https://github.com/fabiopjve/VHDL/tree/master/FPz8

FPz8 at Opencores.org:

http://opencores.org/project,fpz8